计算机组成原理(6) |

您所在的位置:网站首页 › int n指令的执行过程 › 计算机组成原理(6) |

计算机组成原理(6)

|

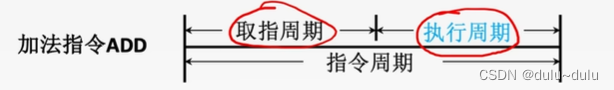

目录 1.指令周期的概念 2.指令周期的数据流 (1)取指周期 (2)间址周期 (3)执行周期 (4)中断周期 3.指令执行方案 (1)单指令周期 (2)多指令周期 (3)流水线方案 1.指令周期的概念指令周期:CPU从主存中每取出并执行一条指令所需的全部时间。 如下图所示,对指令译码就是分析指令的过程

机器周期:一个指令周期常常用若干机器周期来表示,机器周期又叫CPU周期。 时钟周期:一个机器周期又包含若干时钟周期(也称为节拍、T周期或CPU时钟周期,它是CPU操作的最基本单位) 注:CPU上标注的主频,例如主频=3.0GHz,就表示每秒钟可以发送3.0G次的时钟周期

① 如上图所示,一个节拍内可以并行完成多个"相容的"微操作,若两个微操作的执行不会相互冲突,制约,就可以把他们放在同一个节拍内完成。 ② 同一个微操作可能再不同指令的不同阶段被使用,例如(PC)--->MAR这个微操作,在所有指令的取指阶段都会被使用,现在不懂没关系,往后面看。 ③ 不同指令的执行周期所需节拍数各不相同。为了简化设计,选择定长的机器周期,以可能出现的最大节拍数为准(通常以访存所需节拍数作为参考,因为访存时间较长)。 ④ 若实际所需节拍数较少,可将微操作安排在机器周期末尾几个节拍上进行。 每个指令周期内机器周期数可以不等,每个机器周期内的节拍数(时钟周期)也可以不等。例如: ① 对于空指令的执行,当CPU取指,分析这是一条空指令后,这条指令就结束了,就会继续执行下一条指令。所以取指周期(包含分析指令)就是整个指令周期。

② 对于加法指令的执行,当CPU取指,分析这是一条加法指令后,继续执行指令,这条指令周期分为两个机器周期,机器周期内的节拍数可能是不等的。

③ 对于乘法指令的执行,当CPU取指,分析这是一条乘法指令后,继续执行指令,乘法指令的执行本质上是多次的加法和移位,所以取指和执行指令的节拍数可能不等。

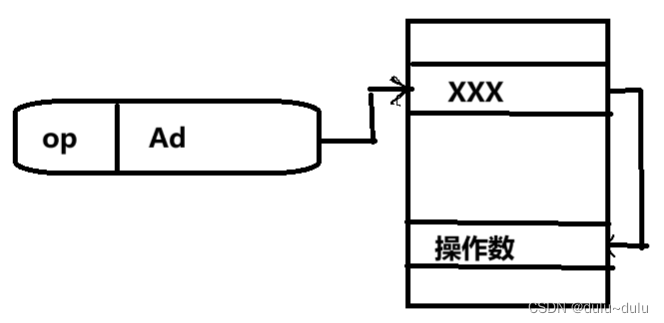

④ 对于具有间接寻址的指令的执行,间接寻址指的是指令的地址码指向的主存地址中的数据才是最终的操作数的地址。

当CPU取指,分析这是一条具有间接寻址的指令后,还需要将指令中包含的形式地址翻译成最终的有效地址,这段时间称为间址周期,接下来才能继续执行指令。可以看到这条指令包含3个机器周期。

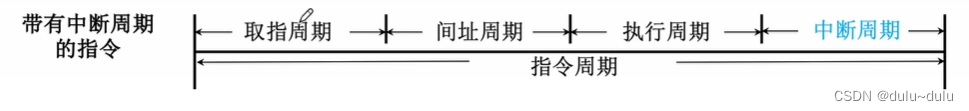

⑤ 对于带有中断周期的指令的执行,执行完指令后,还需检查是否有中断信号需要处理,这段时间称为中断周期,除非CPU处于关中断的状态,否则每执行完一条指令,都需要留出一个机器周期处理中断信号。

所以总结下来,指令周期流程如下:

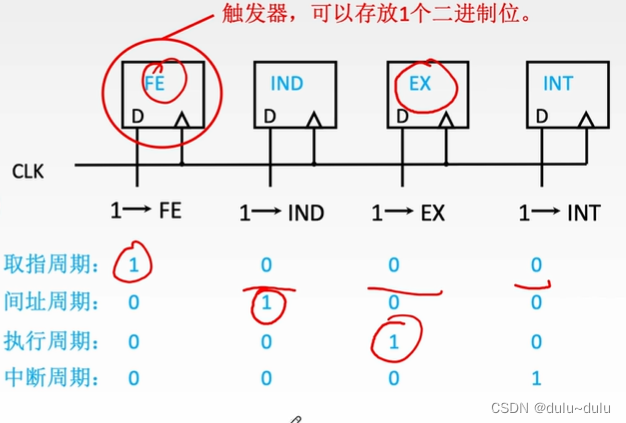

如何判断此时处于哪一个周期呢? 通常会设置触发器,触发器可以存放1个二进制位。如下图所示,每一个周期都会设置对应的触发器,若处于取指周期,那么控制单元就会将FE触发器设为1,其余触发器设为0,表示此时处于取指周期,其他同理。

四个工作周期都有CPU访存操作,只是访存的目的不同。取指周期是为了取指令,间址周期是为了取有效地址,执行周期是为了取操作数,中断周期是为了保存程序断点。 所以根据指令的操作码,根据触发器的信息判断当前处于哪一个机器周期,根据节拍信号判断当前处于这一机器周期的第几个节拍,再根据机器状态条件(PSW)就可以确定现在这个节拍下应该发出哪些"微命令"。 2.指令周期的数据流 (1)取指周期•当前指令地址送至存储器地址寄存器,记做:(PC)--->MAR •CU发出控制信号,经控制总线传到主存,这里是读信号,记做:1--->R 注:主存储器会留两个接口,一个接口表示读,一个接口表示写,若此时要进行读,则读接口置1,所以记1--->R

•将MAR所指主存中的内容经数据总线送入MDR,记做:M(MAR)--->MDR

•将MDR中的内容(此时是指令)送入IR,记做:(MDR)--->IR

•CU发出控制信号,形成下一条指令地址,记做:(PC)+1--->PC

•将指令的地址码送入MAR,记做:Ad(IR)---> MAR(将当前指令的地址码送到MAR中) 或Ad(MDR)--->MAR(把MDR的地址信息送到MAR中,因为在间址周期之前,经过了取指阶段,取址阶段指令先从主存储器取出到MDR,再从MDR传送到 IR 中,所以MDR存放的也是当前指令) •CU发出控制信号,启动主存做读操作,记做:1--->R

•将MAR所指主存中的内容经数据总线送入MDR,记做:M(MAR)--->MDR 到这一步,MDR存放的是操作数的有效地址

•将MDR的数据传送到MAR,这次传送的是操作数的地址,主存储器就可以通过MAR的地址找到存储单元对应数据,传到MDR中。 还有另一种方法,就是将MDR中的有效地址传送至指令的地址码字段,将原来的形式地址覆盖,记作:(MDR)--->Ad(IR),IR中的地址现在就是有效地址,再传入MAR中,此时间接寻址就变为了直接寻址的方式。

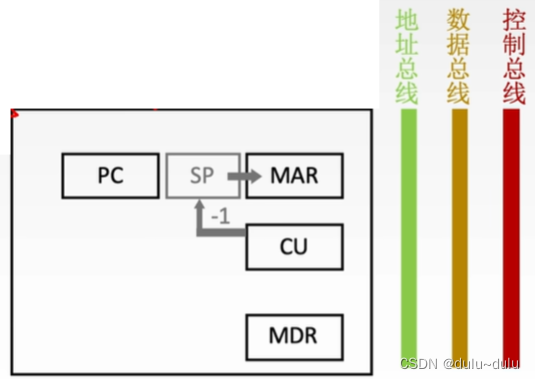

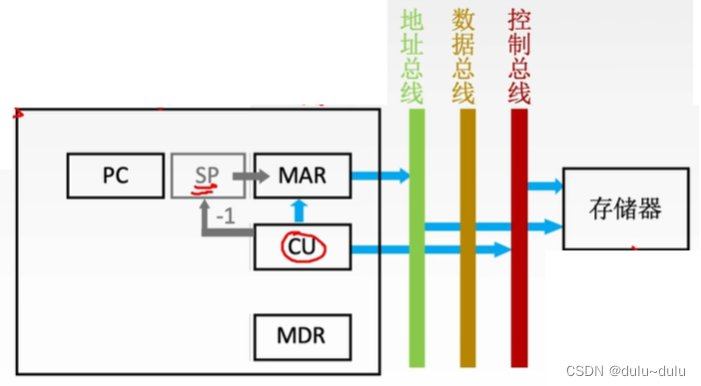

执行周期的任务是根据IR中的指令字的操作码和操作数通过ALU操作产生执行结果不同指令的执行周期操作不同,因此没有统一的数据流向。 (4)中断周期中断就是暂停当前任务去完成其他任务。为了能够恢复当前任务,需要保存断点。一般使用维栈来保存断点,这里用SP表示栈顶地址,假设SP指向栈顶元素,进栈操作是先修改指针,后存入数据。 如图所示,栈顶在低地址一端,若想记录下程序断点的地址,则需要先将SP-1,接着在SP-1的位置,记录断点的地址,当处理完中断信号后,返回断点地址继续处理程序。

•CU控制将SP-1,修改后的地址送入MAR,用来指明把PC值存到哪一个主存单元中。记作:(SP)- 1--->SP,(SP)--->MAR

本质上是将断点存入某个存储单元,假设其地址为a,故可记做:a--->MAR,由于SP的加减都是由CU控制的,所以某些书上也简化为下图,就是CU将当前的栈顶地址送到MAR中。

•CU发出控制信号,启动主存做写操作,记作:1-->W

根据MAR的地址信息,主存储器就能知道往什么地址进行写操作

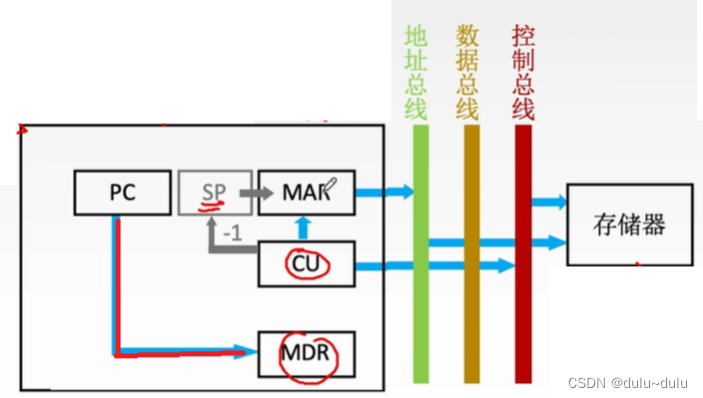

•将断点(PC内容)送入MDR,记做:(PC)--->MDR

现在执行写操作的地址信息保存在MAR中,数据信息保存在MDR中,主存往对应地址写入数据即可

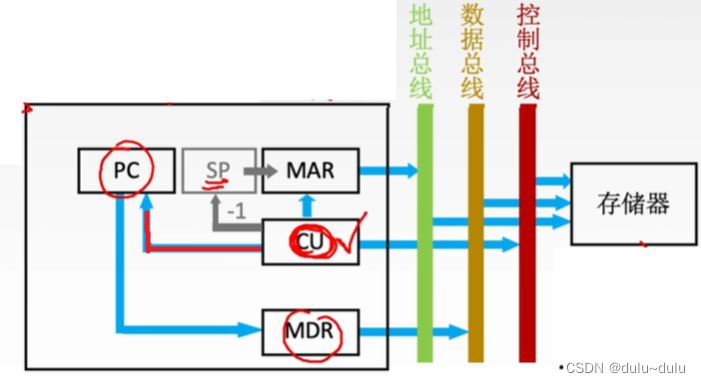

•保存PC值之后,需要修改PC的值,使其指向中断处理程序的第一条指令。

CU控制将中断服务程序的入口地址(由向量地址形成部件产生)送入PC,记作:向量地址--->PC

一个指令周期通常要包括几个时间段(执行步骤),每个步骤完成指令的一部分功能,几个依次执行的步骤完成这条指令的全部功能。

对于单指令周期,每条指令的指令周期都是相同的,也就是某些用较短时间就能完成的指令,需要延长到与最长时间完成的指令一样长的时间。这就意味着某些执行很快的指令,可能有很长的时间是浪费了的。 但这样设计的好处是设计指令执行的控制电路时,只需要根据节拍数就可以判断一条指令是否执行结束,因为一条指令执行的节拍数是一样的。这样控制电路设计起来就会方便些。 若采用单指令周期,各个指令之间是串行执行的:指令周期取决于执行时间最长的指令的执行时间。 优点:控制电路设计较简单。 缺点:对于那些本来可以在更短时间内完成的指令,要使用这个较长的周期来完成,会降低整个系统的运行速度。 (2)多指令周期对不同类型的指令选用不同的执行步骤来完成。指令之间串行执行;可选用不同个数的时钟周期来完成不同指令的执行过程。这就需要更复杂的硬件设计。 优点:整个系统的运行速度相比于单指令周期快很多。 缺点:需要更复杂的硬件设计。 (3)流水线方案在每一个时钟周期启动一条指令,尽量让多条指令同时运行,但各自处在不同的执行步骤中。 所以指令之间并行执行。意思大致如下图所示:

|

【本文地址】

今日新闻 |

推荐新闻 |